数字电路与系统备忘

本文最后更新于 2025年12月28日 晚上

学习数字电路与系统时提炼的备忘,供大家学习

数字电路与系统备忘

绪论、数制、编码

进制转换

- 二、六、八、十六

- 分组对应、等指代替

- 任意进制的转化、

- 按权展开

- 小数部分和整数部分(eg:整数/2取余 小数*2取整 整数自下而上 小数自上而下)

原码、反码、补码

- 原码:

- 最高位表示正负:0表示正,1表示负

- 其余各位表示数的绝对值

- 反码 :

- 正数的反码和原码一样,负数的反码是对原码的绝对值位域取反

- 补码:

- 正数的补码和原码一样,负数的补码是反码+1

格雷码

- 性质:单位距离 循环相邻 无权码 镜面对称

逻辑代数基础及逻辑门电路

逻辑运算

- 与或非 真值表 表示符号

- 基本公式(考察应用)分配律 DeMorgan律

- 定理(代入、反演、对偶)

- 代入定理:函数换变量,等式不会变

- 反演定理: +与*互换、0与1互换、x与 互换,表达式取反

- 对偶定理: +与*互换、0与1互换,表达式变为对偶表达式。二次对偶表达式即原表达式

- 代入定理:函数换变量,等式不会变

- 异或、同或

因果互换律 01律 奇偶律

逻辑表达式的表示

- 逻辑表达式 真值表 卡诺图 逻辑图 波形图的互化

标准与或表达式和标准或与表达式

- 标准与或表达式(最小项之和)

- 从真值表求标准与或表达式:在真值表找到使逻辑函数Y为1的变量取值集合,然后相“或”

eg: - 从一般与或表达式求标准与或表达式:利用

- 从真值表求标准与或表达式:在真值表找到使逻辑函数Y为1的变量取值集合,然后相“或”

- 标准与或表达式(最大项之积)

- 从真值表求标准与或表达式:在真值表找到使逻辑函数Y为0的变量取值集合,然后相“与”

- 注意最大项编号 / 变量取值 的对应关系(和正常的权值运算相同)

- 从真值表求标准与或表达式:在真值表找到使逻辑函数Y为0的变量取值集合,然后相“与”

- 标准与或表达式和标准与或表达式互补

卡诺图——用来化简逻辑函数

规则:不重不漏 尽可能大 每次至少应该包含新一个

- 用最小项卡诺图化简法求 最简与或表达式—圈1

- 用最大项卡诺图化简法求 最简或与表达式—圈0

逻辑函数形式的转换(从与或表达式)

注:求反就是画 ,反函数就是利用反演定理

-

与非——与非

两次求反 再使用DeMorgan公式 -

与或非

求反函数的最简与或表达式,再求反 -

或非——或非

先求出反函数的最简与或表达式,然后反演得到原函数的或与表达式,在两次求反,利用DeMorgan公式

-

化为最小项之和

-

化为最大项之积

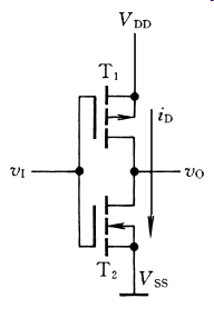

CMOS逻辑门

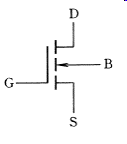

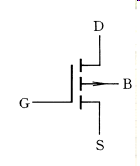

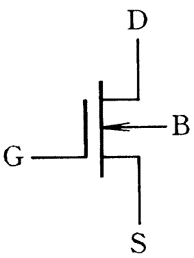

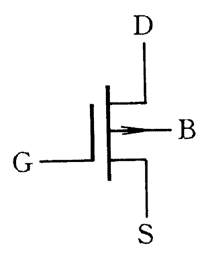

MOS管的四种类型(增强离散,N向内)

-

N沟道增强型

-

P沟道增强型

-

N沟道耗尽型

-

P沟道耗尽型

CMOS逻辑门

非门(给箭头方向相反的电流就是导通,方向相同就是截止)

组合逻辑电路分析与设计

组合逻辑电路 — 功能上无记忆,结构上无反馈

组合逻辑电路

组合逻辑的电路的分析

- 分析步骤:

组合逻辑的电路设计方法

- 设计步骤 :

逻辑电路模块 (理解功能+典型应用+扩展方法)

编码器

-

对于每一个有效的输入信号,产生一组二进制代码

-

8线-3线 优先编码器74148(输入、输出使能信号和输出扩展信号)

-

74HC148(使能输入端、片选输入端,使能输入端,扩展输入端)

-

扩展:74148扩展为16线-4线有限编码器

译码器

-

分为二进制全译码器和部分译码器

-

3线-8线 译码器 74138 ( 为使能端,又叫做片选,可以消除干扰,功能扩展)

-

4线8421BCD码译码器 7442

-

七段显示译码器 7448

数据选择器

-

双4选1数据选择器 74LS153

-

用具有n位地址输入的数据选择器,可以产生任何形式输入变量数不大于n+1的组合逻辑函数

数值比较器

- 串联扩展:低位模块将比较结果馈入高位模块的级联输入端

加法器

-

半加器、全加器

-

超前进位加法器

触发器与存储器

-

存储单元(触发器) 寄存器:一组触发器 存储器:存储大量数据

-

触发器

电路结构: 基本、同步、主从、边沿

触发方式:电平、脉冲、脉冲边沿触发逻辑功能 :RS、JK、D和T触发

-

存储器 RAM(Radom Access Memory) ROM(Read Only Memory)

-

时序逻辑的表示方法

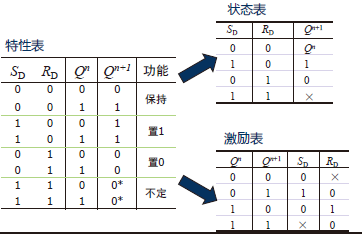

- 特性表(逻辑功能表):含有状态变量的真值表,可以转换为两种形式——状态表和激励表

- 状态方程:含有状态变量的逻辑表达式,有状态方程和激励方程两种形式

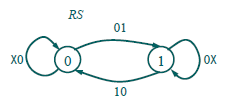

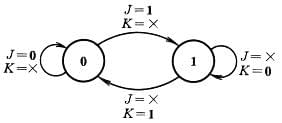

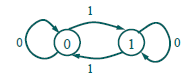

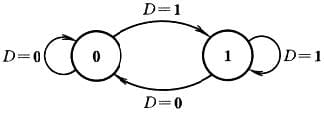

- 状态转移图

- 波形图

- 特性表(逻辑功能表):含有状态变量的真值表,可以转换为两种形式——状态表和激励表

- SR锁存器(基本RS触发器)

- 电平触发的触发器(同步SR)电平触发的触发器(同步D)

- 脉冲触发的主从触发器

- 主从SR触发器

- 主从JK触发器

- 边沿触发器 always @ ( posedge clock ) begin … end ;“>” 表示边沿触发动作

- 边沿D触发器——D-FF的特性

分类

按逻辑功能分

-

SR触发器

-

-

-

SR锁存器、同步、主从

-

-

SR触发器

- 主从、边沿

-

T触发器

-

D触发器

- 边沿、电平触发

按触发方式分

| 无触发 | 只有输入决定保持什么状态,无需触发 | SR锁存 | |

| 电平触发(增加触发) | 1.触发信号CLK有效时,才能够接受输入信号 2.CLK=1期间可能有多次翻转 | 同步SR触发器 | 电平触发D触发器 |

| 脉冲触发(主从触发)(克服反转多次) | 利用主从触发便有每个CLK周期输出(从)只改变一次,CLK回到低电平输出状态才改变 | 主从SR触发器 | 主从JK触发器 |

| 边沿触发(克服只取决于下降时刻问题) | 输出的状态仅取决于CLK上升沿或者下降沿到达时刻输入信号的状态 | 边沿D触发器 | 下降边沿JK触发器 |

时序逻辑电路分析与设计

时序逻辑电路

-

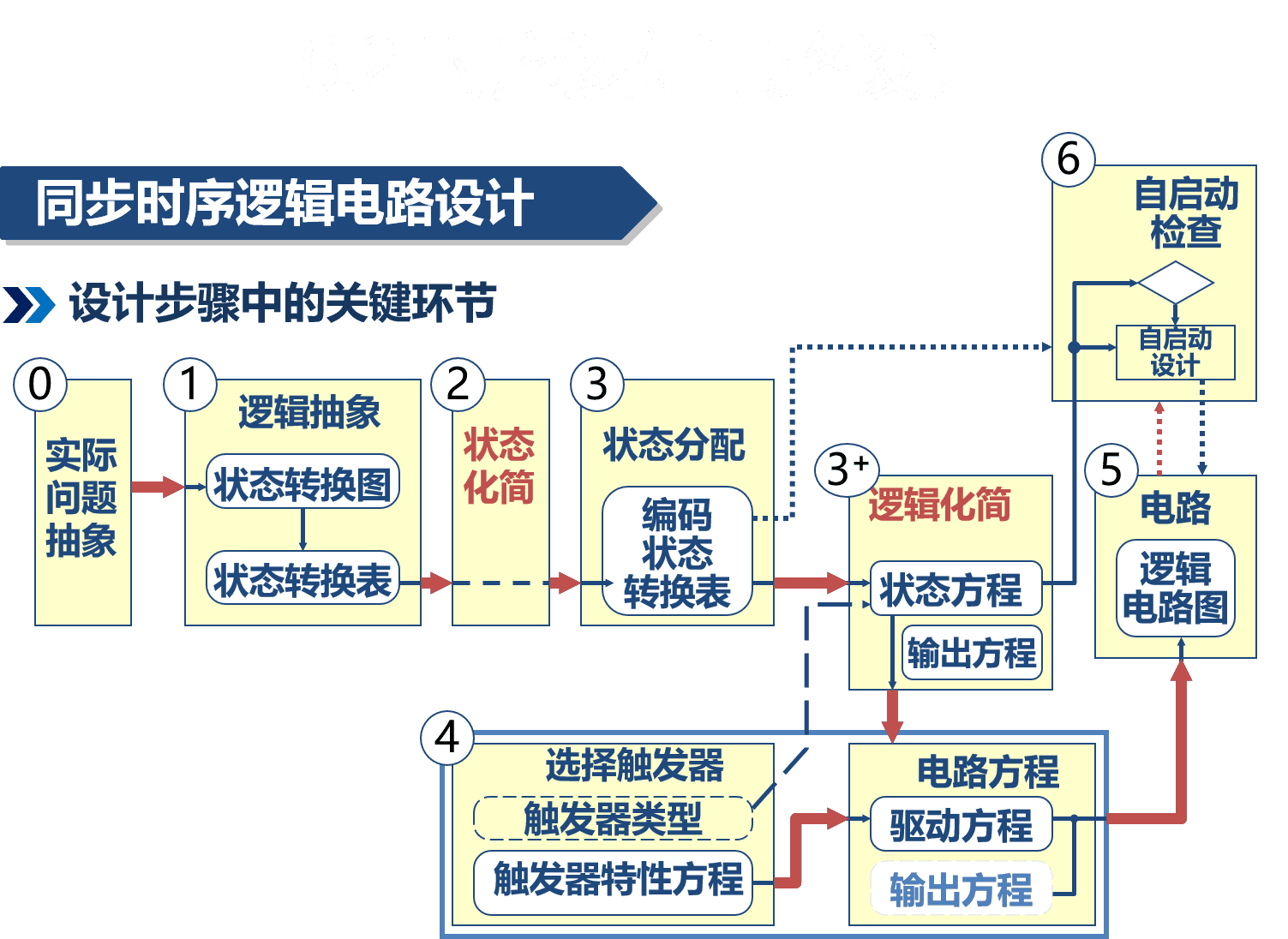

同步时序逻辑电路的分析

分析步骤:

根据给定的时序电路图写出个逻辑方程式:驱动方程、状态方程(将驱动方程代入到触发器的特性方程)、输出方程→根据状态方程和输出方程,列出时序电路的状态转换表,画出住状态转换图或时序图→根据电路的状态转换图或时序图,说明给定时序逻辑电路的逻辑功能

-

同步时序逻辑电路的设计(能否自启动)

Verilog

-

什么是FPGA(现场可编程门阵列)

-

Verilog描述级别 可综合性

-

行为级/算法级(不一定可综合)

-

RTL级(可综合)

-

门级/结构级(可综合)

-

开关级/物理级

-

-

综合:即通过特定的软件将Verilog代码转换成门级描述,并能下载到硬件平台里。

模块填空

- 基本语法:

-

wire和reg

- 所有的输入信号都需要定义成wire型,或者不定义(使用缺省类型)

- 对于内部信号,如果使用assign进行赋值则定义成wire型,如果使用always块进行赋值则必须定义成reg型

- 寄存器的输出必须定义成reg型

-

赋值

- 非阻塞赋值<=:(时序逻辑电路中使用!!)

- 在时序逻辑中,一个非阻塞赋值代表一个D触发器。

- 块结束后,赋值动作才能完成,因此上面语句所赋的变量值不能立刻为下面语句使用。

- 在时序逻辑中,块语句中的各个赋值语句之间没有先后顺序

- 阻塞赋值=:(组合逻辑电路)

- 赋值动作立刻完成

- 组合逻辑电路中,块语句中的各个赋值语句之间没有先后顺序

- 非阻塞赋值<=:(时序逻辑电路中使用!!)

-

assign always 敏感变量

-

always组合逻辑电路:

- 将所有有敏感变量列在敏感变量列表中(各敏感变量之间用or或者“,”隔开。可用“*”代替所有敏感变量)

- 用阻塞赋值

- 条件语句的完全描述(即每一个if均需要else与之对应,每一个case分支都需要有描述)

-

always时序逻辑电路:

- 只有时钟信号和复位信号可以放在敏感列表里,并且必须附带posedge和negedge

- 利用非阻塞赋值

- 对于未描述的分支,变量将保持原值

-

-

FSM的设计方法

-

数字系统的工作时钟

- D触发器的动态特性(建立时间 保持时间 传输时间)T>=传输时间+建立时间

- 时间延迟 # 组合逻辑的延迟T >=传输时间 + 建立时间 + 组合逻辑延迟

- 提高系统工作时间的方法—— 流水线 总处理数据的吞吐量增加

- D触发器的动态特性(建立时间 保持时间 传输时间)T>=传输时间+建立时间

FSM的设计方法

一段式状态机 (单always块结构)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

always @(posedge clk or posedge rst) begin

if(rst)

FSM <= S0

else begin

case(FSM)

S0:begin

Out_0; //输出

if(condition1) FSM<= S1;//状态转移

else if (condition2) FSM<= S2;//状态转移

…

end

S1:begin

Out_1; //输出

if(condition3) FSM<= S3;//状态转移

else if (condition4) FSM <=S4;

…

end

……

default: begin

Out_0; //输出

if(condition0) FSM<= S0;//状态转移

end

endcase

end

end

- 单 always 块把组合逻辑和时序逻辑放在一个时序 always 块描述。输出时为寄存器输出,所以无毛刺。但是这种方式会产生多余的触发器(因为把组合逻辑也放在时序逻辑中实现),而且代码难以修改调试。对于那些简单的状态机,一段式方便理解。但是对于复杂状态机,代码难于更改,条件复杂带来电路开销大,工作性能(电路最高频率)亦受限,因此实际中这种结构很少使用。

两段式状态机 (双always块结构)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

//时序逻辑,这段一般是不变的,描述从现态转移到次态

always @ (posedge clk or posedge rst ) begin

if(rst)

current_state <= S0;

else

current_state<=next_state;

end

//组合逻辑,包括转移条件以及输出

always @ (current_state) begin

case(current_state)

S0:begin

Out_0; //输出

if(condition1) next_state <= S1;//状态转移

else if (condition2) next_state <= S2;//状态转移

else next_state <= S0;

end

S1:begin

Out_1; //输出

if(condition3) next_state <= S3;//状态转移

else if (condition4) next_state <=S4;

…

end

……

default: begin

Out_0; //输出

if(condition0) next_state <= S0;//状态转移

end

endcase

end

二段式中,一个always块采用同步时序描述状态转移;另一个采用组合逻辑判断转移条件,以及描述输出。二段式便于阅读,理解和维护,有利于综合出更少的资源。但是由于采用的是组合逻辑输出,容易产生毛刺,且不利于约束,也不利于布局布线。

三式状态机 (三always块结构)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

//第一个always块,时序逻辑,描述现态转移到次态

always @ (posedge clk or negedge rst) begin

if(rst_n)

current_state<=S0;

else

current_state<=next_state;

end

//第二个always块,组合逻辑,描述状态转移的条件

always @ (current_state) begin

case(current_state)

S0:begin

if(condition1) next_state <= S1;//状态转移

else if (condition2) next_state <= S2;//状态转移

else next_state <= S0;

end

S1:begin

if(condition3) next_state <= S3;//状态转移

else if (condition4) next_state <=S4;

…

end

……

default: begin

if(condition0) next_state <= S0;//状态转移

end

endcase

end

//第三个always块,时序逻辑,描述输出

always @ (posedge clk or negedge rst) begin

if(rst)

out0;

else

case(current_state)

S0: out0;

S1: out1;

….

default:Out0;

endcase

end

- 三段式结构中,2个时序always块分别用来描述状态跳转和输出。组合always块用于描述状态转移条件。虽然使用的硬件资源较多,但输出采用寄存器结构,无毛刺,而且代码更清晰易读,对于复杂的状态机来说逻辑清晰,是一种比较流行的状态机结构。

高层次设计

-

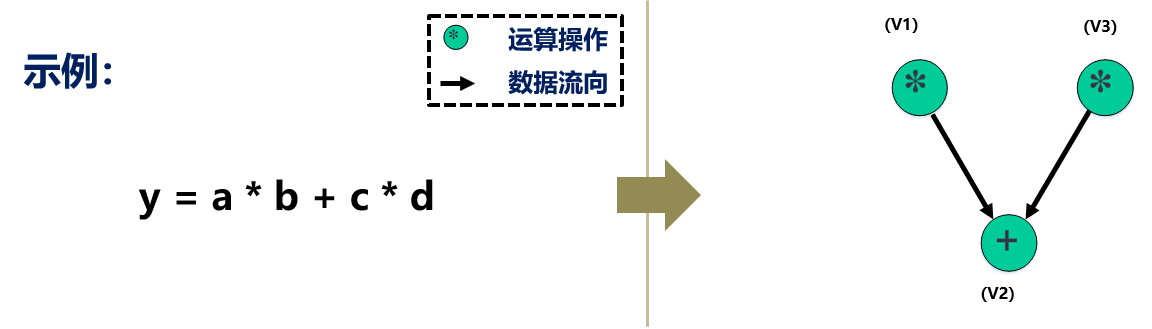

数据流图

-

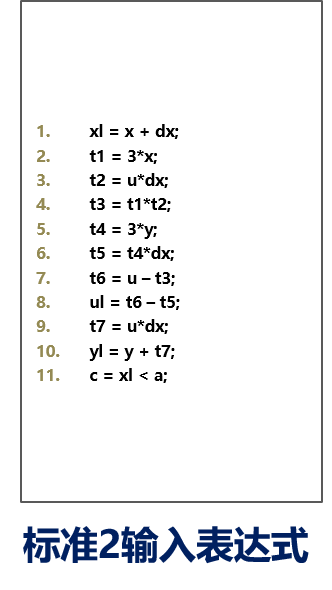

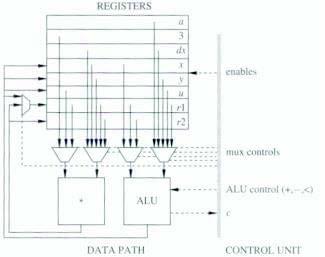

构建步骤 :取出核心代码→算法拆分为标准2输入表达式→根据标准2输入表达式构建数据流图

-

简单算子调度(Schedule)复用的代价:选择器更复杂

-

受限调度

-

左边缘算法——间隔图、间隔表 着色

-

-

资源绑定

-

数据路径

其他

兰特规则:, 针脚数, 门数量